User:John R. Brews/Sample2

Pole splitting is a phenomenon exploited in some forms of frequency compensation used in an electronic amplifier. When a capacitor is introduced between the input and output sides of the amplifier with the intention of moving the pole lowest in frequency (usually an input pole) to lower frequencies, pole splitting causes the pole next in frequency (usually an output pole) to move to a higher frequency. This pole movement increases the stability of the amplifier and improves its step response at the cost of decreased speed.[1][2][3][4]

Example of pole splitting

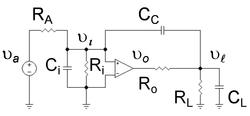

This example shows that introduction of the capacitor referred to as CC in the amplifier of Figure 1 has two results: first it causes the lowest frequency pole of the amplifier to move still lower in frequency and second, it causes the higher pole to move higher in frequency.[5] The amplifier of Figure 1 has a low frequency pole due to the added input resistance Ri and capacitance Ci, with the time constant Ci ( RA // Ri ). This pole is moved down in frequency by the Miller effect. The amplifier is given a high frequency output pole by addition of the load resistance RL and capacitance CL, with the time constant CL ( Ro // RL ). The upward movement of the high-frequency pole occurs because the Miller-amplified compensation capacitor CC alters the frequency dependence of the output voltage divider.

The first objective, to show the lowest pole moves down in frequency, is established using the same approach as the Miller's theorem article. Following the procedure described in the article on Miller's theorem, the circuit of Figure 1 is transformed to that of Figure 2, which is electrically equivalent to Figure 1. Application of Kirchhoff's current law to the input side of Figure 2 determines the input voltage to the ideal op amp as a function of the applied signal voltage , namely,

which exhibits a roll-off with frequency beginning at f1 where

which introduces notation for the time constant of the lowest pole. This frequency is lower than the initial low frequency of the amplifier, f0<?sub> say, which for CC = 0 F is:

Turning to the second objective, showing the higher pole moves still higher in frequency, it is necessary to look at the output side of the circuit, which contributes a second factor to the overall gain, and additional frequency dependence. The voltage is determined by the gain of the ideal op amp inside the amplifier as

Using this relation and applying Kirchhoff's current law to the output side of the circuit determines the load voltage as a function of the voltage at the input to the ideal op amp as:

This expression is combined with the gain factor found earlier for the input side of the circuit to obtain the overall gain as

This gain formula appears to show a simple two-pole response with two time constants. (It also exhibits a zero in the numerator but, assuming the amplifier gain Av is large, this zero is important only at frequencies too high to matter in this discussion , so the numerator can be approximated as unity.) However, although the amplifier does have a two-pole behavior, the two time-constants are more complicated than the above expression suggests because the Miller capacitance contains a buried frequency dependence that has no importance at low frequencies, but has considerable effect at high frequencies. That is, assuming the output R-C product, CL ( Ro // RL ), corresponds to a frequency well above the low frequency pole, the accurate form of the Miller capacitance must be used, rather than the Miller approximation. According to the article on Miller effect, the Miller capacitance is given by

(For a positive Miller capacitance, Av is negative.) Upon substitution of this result into the gain expression and collecting terms, the gain is rewritten as:

with Dω given by a quadratic in ω, namely:

Every quadratic has two factors, and this expression looks simpler if it is rewritten as

where and are combinations of the capacitances and resistances in the formula for Dω.[6] They correspond to the time constants of the two poles of the amplifier. One or the other time constant is the longest; suppose is the longest time constant, corresponding to the lowest pole, and suppose >> . (Good step response requires >> . See Selection of CC below.)

At low frequencies near the lowest pole of this amplifier, ordinarily the linear term in ω is more important than the quadratic term, so the low frequency behavior of Dω is:

where now CM is redefined using the Miller approximation as

which is simply the previous Miller capacitance evaluated at low frequencies. On this basis is determined, provided >> . Because CM is large, the time constant is much larger than its original value of Ci ( RA // Ri ).[7]

At high frequencies the quadratic term becomes important. Assuming the above result for is valid, the second time constant, the position of the high frequency pole, is found from the quadratic term in Dω as

Substituting in this expression the quadratic coefficient corresponding to the product along with the estimate for , an estimate for the position of the second pole is found:

and because CM is large, it seems is reduced in size from its original value CL ( Ro // RL ); that is, the higher pole has moved still higher in frequency because of CC.[8]

In short, introduction of capacitor CC moved the low pole lower and the high pole higher, so the term pole splitting seems a good description.

Selection of CC

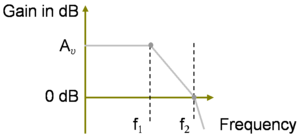

What value is a good choice for CC? For general purpose use, traditional design (often called dominant-pole or single-pole compensation) requires the amplifier gain to drop at 20 dB/decade from the corner frequency down to 0 dB gain, or even lower.[9][10] With this design the amplifier is stable and has near-optimal step response even as a unity gain voltage buffer. A more aggressive technique is two-pole compensation.[11][12]

The way to position f2 to obtain the design is shown in Figure 3. At the lowest pole f1, the Bode gain plot breaks slope to fall at 20 dB/decade. The aim is to maintain the 20 dB/decade slope all the way down to zero dB, and taking the ratio of the desired drop in gain (in dB) of 20 log10 Av to the required change in frequency (on a log frequency scale[13]) of ( log10 f2 − log10 f1 ) = log10 ( f2 / f1 ) the slope of the segment between f1 and f2 is:

- Slope per decade of frequency

which is 20 dB/decade provided f2 = Av f1 . If f2 is not this large, the second break in the Bode plot that occurs at the second pole interrupts the plot before the gain drops to 0 dB with consequent lower stability and degraded step response.

Figure 3 shows that to obtain the correct gain dependence on frequency, the second pole is at least a factor Av higher in frequency than the first pole. The gain is reduced a bit by the voltage dividers at the input and output of the amplifier, so with corrections to Av for the voltage dividers at input and output the pole-ratio condition for good step response becomes:

Using the approximations for the time constants developed above,

or

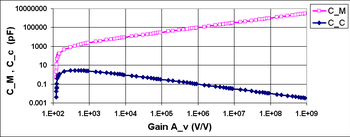

which provides a quadratic equation to determine an appropriate value for CC. Figure 4 shows an example using this equation. At low values of gain this example amplifier satisfies the pole-ratio condition without compensation (that is, in Figure 4 the compensation capacitor CC is small at low gain), but as gain increases, a compensation capacitance rapidly becomes necessary (that is, in Figure 4 the compensation capacitor CC increases rapidly with gain) because the necessary pole ratio increases with gain. For still larger gain, the necessary CC drops with increasing gain because the Miller amplification of CC, which increases with gain (see the Miller equation ), allows a smaller value for CC.

To provide more safety margin for design uncertainties, often Av is increased to two or three times Av on the right side of this equation.[14] See Sansen[4] or Huijsing[10] and article on step response.

Slew rate

The above is a small-signal analysis. However, when large signals are used, the need to charge and discharge the compensation capacitor adversely affects the amplifier slew rate; in particular, the response to an input ramp signal is limited by the need to charge CC.

References and notes

- ↑ That is, the rise time is selected to be the fastest possible consistent with low overshoot and ringing.

- ↑ (2007) C. Toumazu, Moschytz GS & Gilbert B eds: Trade-offs in analog circuit design: the designer's companion. New York/Berlin/Dordrecht: Springer, pp. 272–275. ISBN 1402070373.

- ↑ Marc T. Thompson (2006). Intuitive analog circuit design: a problem-solving approach using design case studies. Amsterdam: Elsevier Newnes, p. 200. ISBN 0750677864.

- ↑ 4.0 4.1 Wally M. C. Sansen (2006). Analog design essentials. New York; Berlin: Springer, §097, p. 266 ff. ISBN 0-387-25746-2.

- ↑ Although this example appears very specific, the associated mathematical analysis is very much used in circuit design.

- ↑ The sum of the time constants is the coefficient of the term linear in jω and the product of the time constants is the coefficient of the quadratic term in (jω)2.

- ↑ The expression for differs a little from ( CM+Ci ) ( RA // Ri ) as found initially for f1, but the difference is minor assuming the load capacitance is not so large that it controls the low frequency response instead of the Miller capacitance.

- ↑ As an aside, the higher the high-frequency pole is made in frequency, the more likely it becomes for a real amplifier that other poles (not considered in this analysis) play a part.

- ↑ A.S. Sedra and K.C. Smith (2004). Microelectronic circuits, Fifth Edition. New York: Oxford University Press, p. 849 and Example 8.6, p. 853. ISBN 0-19-514251-9.

- ↑ 10.0 10.1 Huijsing, Johan H. (2001). Operational amplifiers: theory and design. Boston, MA: Kluwer Academic, §6.2, pp.205–206 and Figure 6.2.1. ISBN 0-7923-7284-0.

- ↑ Dennis Feucht. Two-pole compensation.

- ↑ Douglas Self (2006). Audio power amplifier design handbook. Oxford: Newnes, pp. 191–193. ISBN 0750680725.

- ↑ That is, the frequency is plotted in powers of ten, as 1, 10, 102 etc.

- ↑ A factor of two results in the maximally flat or Butterworth design for a two-pole amplifier. However, real amplifiers have more than two poles, and a factor greater than two often is necessary.

![{\displaystyle =[1+j\omega (C_{L}+C_{C})(R_{o}//R_{L})]\,\!}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a1bb92565d1fcaf5f5135b336a5192d1e2f0db93)

![{\displaystyle \cdot \ [1+j\omega C_{i}(R_{A}//R_{i})]\,\!}](https://wikimedia.org/api/rest_v1/media/math/render/svg/39f29b28ceaca3f424e2725b5be75edefc5c5f0d)

![{\displaystyle {\begin{aligned}\ D_{\omega }&=1+j\omega [(C_{M}+C_{i})(R_{A}//R_{i})+(C_{L}+C_{C})(R_{o}//R_{L})]\\&=1+j\omega (\tau _{1}+\tau _{2})\approx 1+j\omega \tau _{1}\ ,\ \\\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e3b3e5fbf7b09f06e962db1c671b878572cffe4a)

![{\displaystyle {\frac {[(C_{M}+C_{i})(R_{A}//R_{i})+(C_{L}+C_{C})(R_{o}//R_{L})]^{2}}{(C_{C}C_{L}+C_{L}C_{i}+C_{i}C_{C})(R_{A}//R_{i})(R_{O}//R_{L})}}\,\!}](https://wikimedia.org/api/rest_v1/media/math/render/svg/08f35d8a2a8adbee2c46d8380d2179b5fca504fb)